Si基板上にナノ回路を集積する半導体技術は、この30年間ムーアの法則に従い発展してきました。しかし、近年微細化が進むにつれてトランジスタのリーク電流が増えてしまうという弊害が問題となっています。結果として高集積化、高速化が進むにつれて発熱と言う問題が無視できなくなっています。

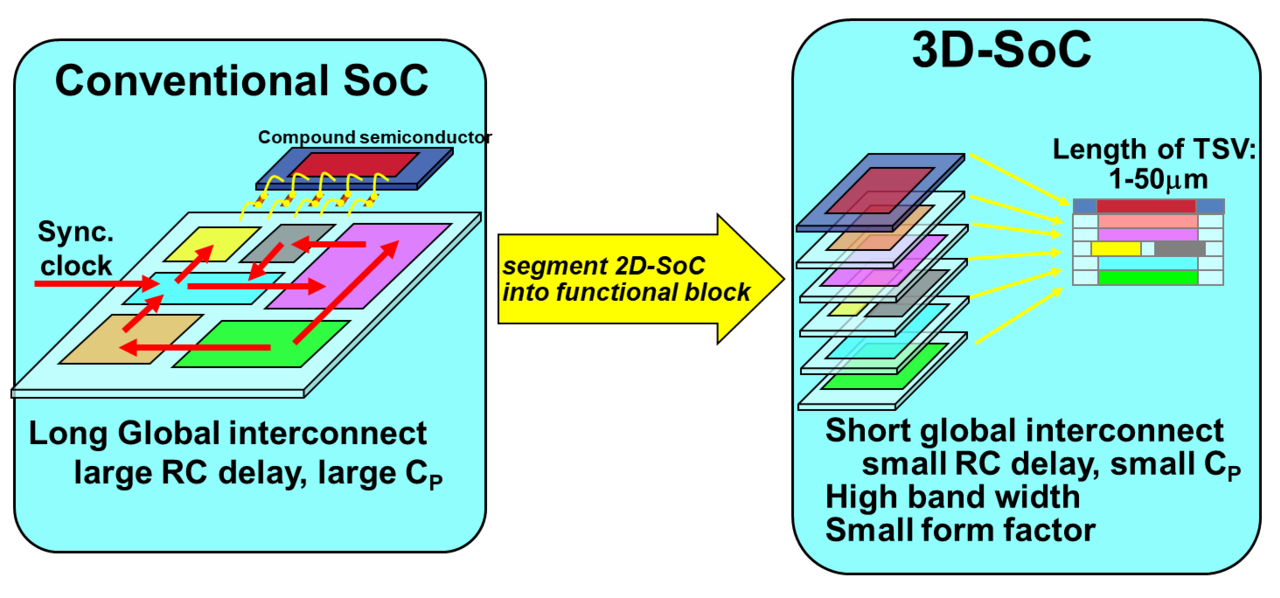

3次元LSI(3D-IC)は微細化技術の新たなブレークスルーとして近年を注目を集めています。すでに幾つかのアプリケーション分野では3D LSI技術(3D-IC)を使った量産チップの生産も始まりました。下図は3D SoCチップの優位点を図示しています。3Dシステムオンチップ(3D SoC)は、2D SoCの機能ブロックを分割して積層し、層間を最短経路で配線することができます。その結果、3D LSI(3D-IC)は対性能消費電力を低く、またフットプリントを小さくすることができます。更に各種ブロックを自由に積層でき、これらブロック間を多数の配線で結ぶことができ、データを高速に送ることができます。さらに、MEMSや化合物半導体も積層することができ、今までのIC単独では実現できなかった機能を持たせることが可能になりつつあります。

3D-IC製造技術は、(1)貫通配線(TSV:Through Silicon Via)形成、(2)バンプ形成、(3)ウエハー薄化、(4)チップ/ウエハーアライメント、および(5)チップ/ウエハー積層の技術から構成されます。東北マイクロテックは東北大学小柳研の協力のもと、先進的な3D-ICプロセスを独自に開発し、これら技術を確立するとともに数々のパテントを有しています。

従来の3D-ICはボンディングパッドの下にパッドと同程度の大きさのスルーホールを形成しています。この方法は既存の2D ICチップレイアウトを少し変更することで積層でき、小型化できるという利点があります。しかし、3D-ICは前述したように、各回路ブロックを多数の配線で積層することにより桁違いに高速にできたり、異種の材料のチップを積層することにより高機能なICキューブが実現できるといったポテンシャルを持っています。3D積層化によってチップ自体のフットプリントかつ性能を改善するためには、層間を制約なく最短距離で自由に配線できることが重要です。東北マイクロテックはこのような層間配線を可能にするため、TSV径を2ミクロン以下に、バンプピッチを5ミクロン以下にするプロセス技術を確立し、積層された各機能ブロックの間を数万本のTSVで配線することを可能としました。その結果、実質的に数十〜百層のブロックを積層してもどの層の間でも制約なく自由に配線することができるようになります。

English Site Menu

Company

Technology

Foundry service

Service case study