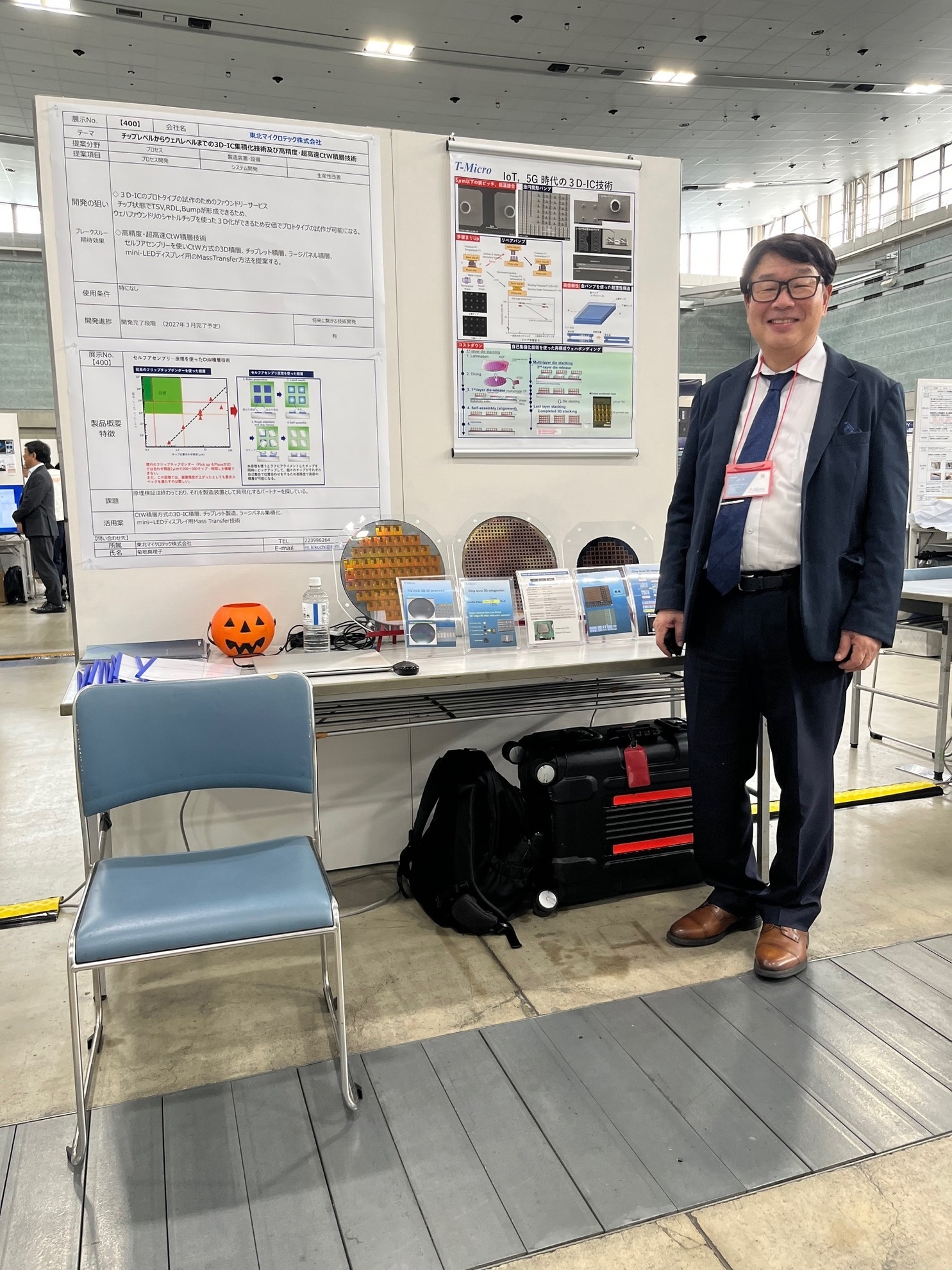

今回は、弊社の Au-Au 超微細マイクロバンプ接合技術 についてご紹介します (^-^)/

---------------------------------------------

(超微細ってどのくらい??)

マイクロバンプの最小サイズは φ3.3 µm、 最小ピッチは 5.6 µm の実績があります。

(接合良品率は??) バンプサイズ φ3.3 µm、ピッチ 7.0 µm、バンプ数 17万 において、 接合評価で100%の良品率を確認しています。 また、バンプサイズ φ5.0 µm、ピッチ 8.0 µm、バンプ数 13.8万 において、 接合良品率99.9%を確認しています。

---------------------------------------- もし技術にご興味を持っていただけましたら、お気軽にお問い合わせください (^o^)/