3D-IC(三次元LSI)の構成・利点

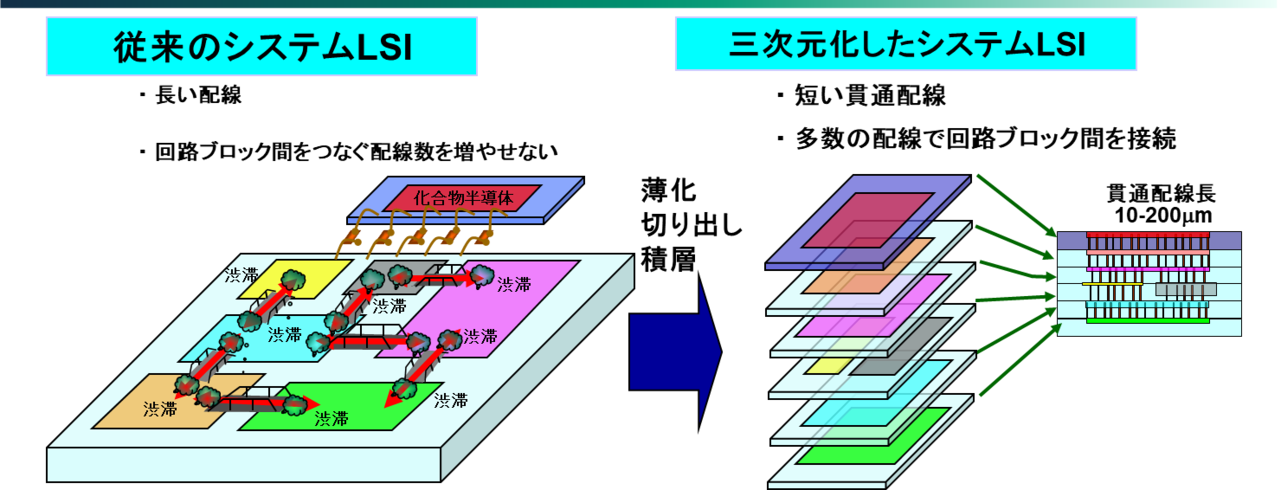

LSI(大規模集積回路)は、メモリ、演算回路、制御回路、入出力回路、センス回路、増幅回路等の回路ブロックから構成されています。一つのチップの中に多くの回路ブロックを入れたSoC(システムオンチップ)やマイクロプロセッサチップでは、多機能化や高速化を目指して開発されてきました。回路規模が大きくなるほどチップ面積は増加し、回路ブロック間の数mmの比較的長い配線でのデータの遅延、電力消費が問題になってきました。3D-IC(三次元LSI)は回路ブロックを構成する部分を別々に切り離し、重ねて、チップ(回路ブロック)間をチップを貫通させた配線(シリコンデバイスの場合はTSV:Through Silicon Via)で接続する構造をもったLSIです。図1に従来のLSIと比較した模式図を示します。データの流れを車の流れに例えるとよくわかります。左の図で回路ブロックを一つの町、この町の間を川が流れており車が通る橋があるとすると交通量の多い時間帯はこの橋の及び近傍で渋滞が発生し、同時にアイドリングで無駄なエネルギーを消費します。データの流れも同じようにこの回路ブロックを接続する長い配線で遅れ無駄なエネルギーを消費します。

図1. 従来のSoC LSIと3D-IC(三次元LSI)の比較

一方右図のような、構造をとると回路ブロック間の配線の長さは、切り出したLSIチップの厚さになります。センサやDRAM等のメモリ以外のMOS型デバイスでは、大部分の電流がSiの深さ2μm程度より深いところは流れないので、理想的にはこの厚さまで薄くすることが可能です。実際には強度、加工時の欠陥、熱伝導を考慮して決められますが二次元的に配置したLSIより1桁以上短くできます。また、回路ブロック間を接続する配線数も2桁以上多く取れるため、並列にデータを送れるようなシステム構成になっていればデータ処理速度は非常に高速になります。逆に処理速度をあまりあげないような設計であれば、消費電力が下がるのでエネルギー効率の良いLSIと言えます。また、図からわかるとおり、チップ面積(投影面積)が下がります。さらに、MEMS(Micro Elctro Mechanical Systems)技術を使って形成するセンサ,アクチュエーター,アンテナ、化合物半導体で作られるRFパワーアンプ,センサ等のデバイスも積層できるため、高機能のSoCが実現できます。

課題

今までは、3D-IC(三次元LSI)の良い点を見てきました。しかし、このような利点を出すためには多くの課題があり、どのような3D-IC(三次元LSI)を作るかによって、最適な構造、製法は大きく変わります。先ず、初めに考慮すべきなのは、貫通配線上およびその周囲数μmの領域には、トランジスタなどの活性素子を置けないことです。先端のトランジスタ素子のサイズは0.1μmを切りますが、現行の貫通配線の直径は10-50μmでこの領域がデッドエリアになります。多くの貫通配線でチップ間を接続するということは、それだけデッドエリアを増やし積層チップの面積効率を下げます。このため、面積効率を変えないで貫通配線本数を増やすには細い貫通配線の接続技術が必要になります。例えば1cmx1cmのチップを100万本の貫通配線で接続し、面積効率のロスを1%以下にするためには、1μm程度の直径の貫通配線が必要になります。また、LSIの配線とは異なり、貫通配線の周囲はシリコンで囲まれているため、寄生容量によるエネルギーロスも無視できません。さらに、主流となっているCuを導電材料としたCu-TSVの場合、半導体の特性劣化を引き起こす銅がトランジスタのすぐそばに位置するため、銅のシリコン中への拡散を抑える構造・技術が必要になります。次に、三次元化をするために、どのような技術や材料が必要かを見ていきます。

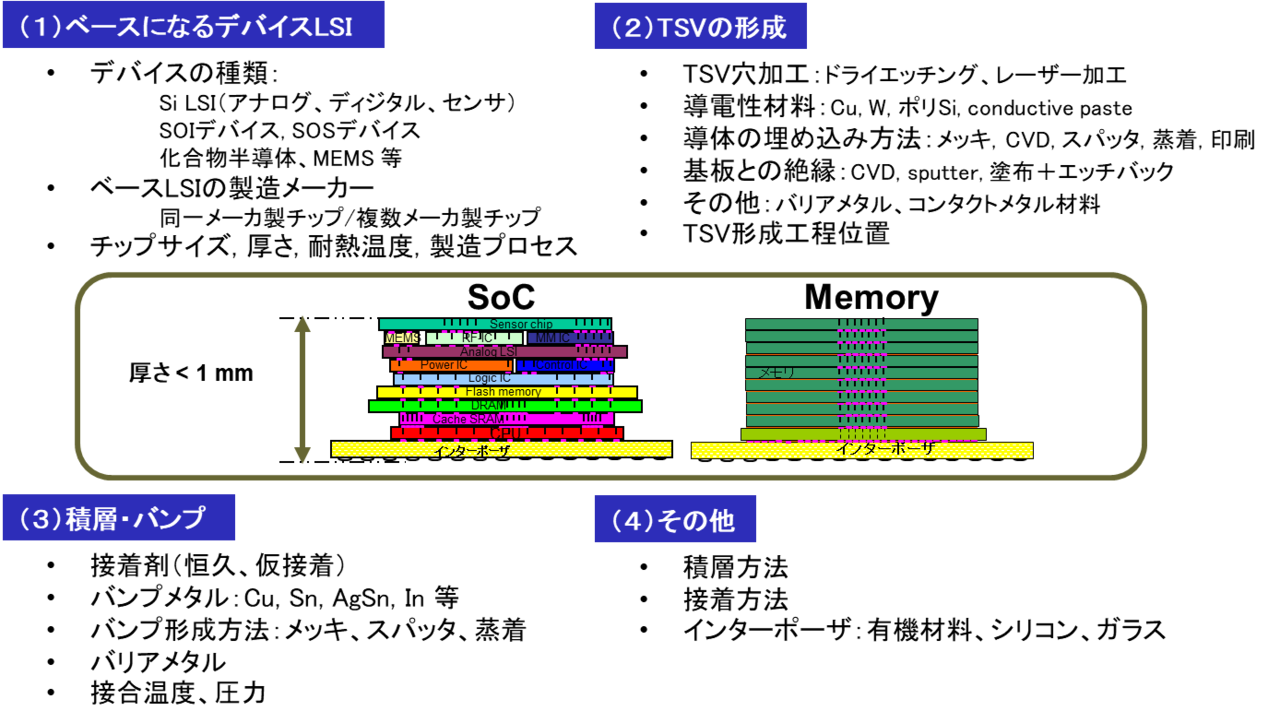

図2に新規技術・材料をまとめました。

図2.3D-IC(三次元LSI)を実現するための技術・材料

TSVプロセス、積層・バンププロセスでいろいろな新構造や新材料が提案されていますが、ここで最も重要なことは、どのようなアプリケーションで使うのか、ベースになるLSIは何か、このサプライチェーンは何かということです。全世界で非常に多くの3D-IC(三次元LSI)の研究開発が行われており、多くの提案がなされています。しかし最適な構造は実現しようとするアプリケーションによって異なり、その実現手段となる技術や材料も変わるため目標システムのイメージがなければ個々の技術の最適化をしても主流から外れる可能性があります。

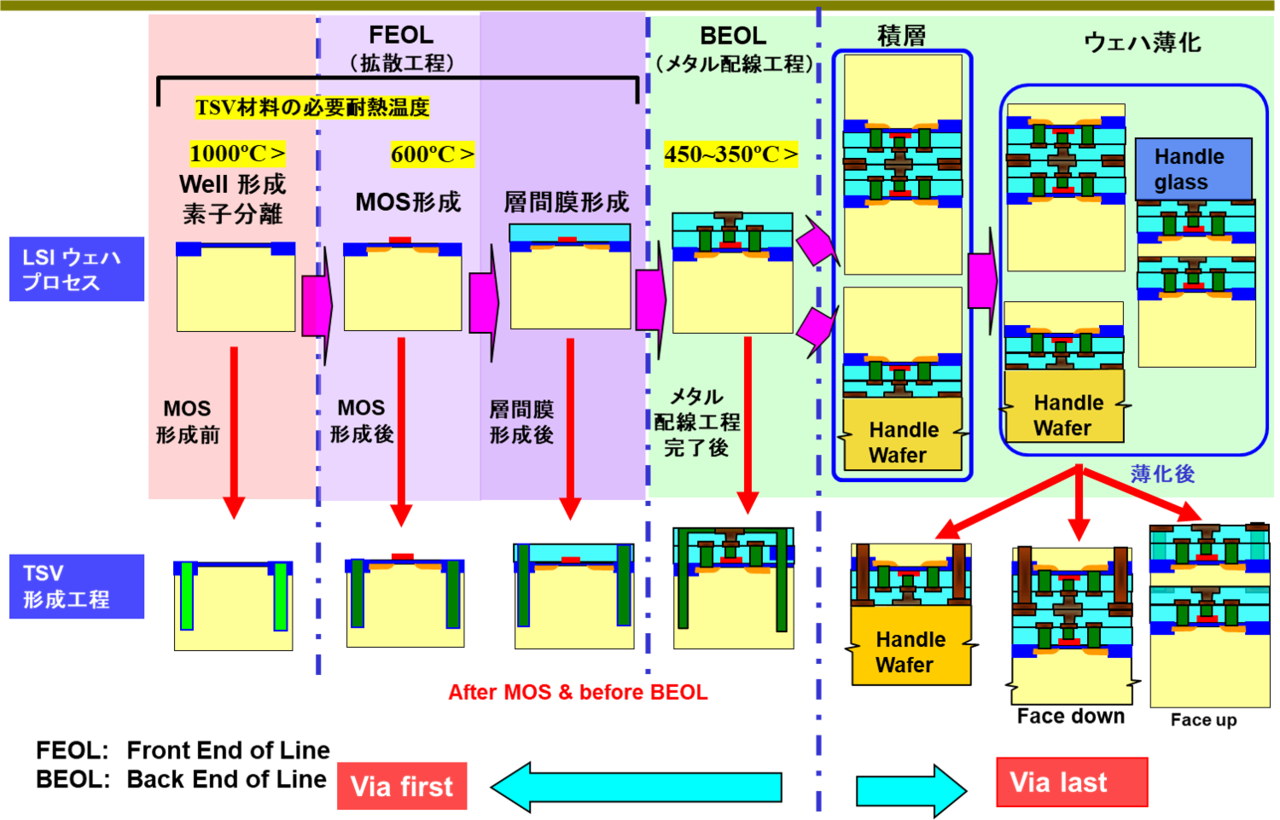

図3にTSV形成プロセスによる分類を示しました。

図3. LSI製造フローとTSV形成プロセス

図に示すように、大きく分けて3種類のTSVの作り方があります。Via First(ビア・ファースト)は、トランジスタ形成工程の前に作りこむ方法で、トランジスタレベルで三次元化可能なので三次元LSI開発の初期から、東北大/小柳等が研究を始めました。ゲート酸化やトランジスタの拡散層の活性化アニール前に形成するため1,000℃程度の温度に耐えることが必要で、導電材料はリンをドープしたポリシリコンです。高品質の絶縁膜が使えるメリットはありますが抵抗率が後述の材料に比べて高いことが欠点です。Via Middle(ビア・ミドル)はMOS形成後から配線工程前(最近では配線工程中というIBMの例もあります)にTSVを作りこむ方式で導電材料は主にW又はCuが使われます。現在は、ファンドリを中心にCuを導電材料に使った開発が進んでいます。この技術は、三次元の専用設計が必要であり、その費用数十億円ということを考慮すると300㎜ウェーハを使った大量生産品がターゲットでなければ採算が合わないように思います。Via Last(ビア・ラスト)は、ウェハ工程を終えたLSIにTSVを形成する方式で、デバイス面からあける方法のFront Via(フロント・ビア)、裏面からあける方法のBack Via(バック・ビア)方式があります。導電材料はCuや導電ペーストが使われます。

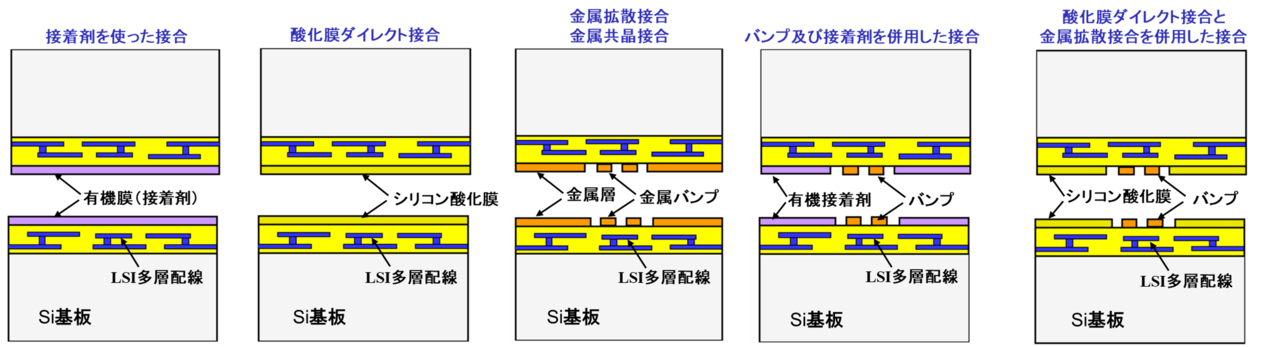

ウェーハまたはチップの積層技術もいろいろな方法が提案されています(図4)。

図4. ウェハ/チップ接合技術

図の左二つは、接合してから、TSVを形成する方式でメタルバンプは使いません。また、ベースLSIにSOIを使うと貫通配線(周りは層間絶縁膜)のサイズを1μm以下にすることが可能です。金属拡散接合および酸化膜ダイレクト接合では非常に強固の接合が得られる一方、表面を清浄にして粗さを1nm以下に抑えることが必要です。金属バンプや共晶結合を使った方式は、他の方式より強度は落ちますがプロセス的に冗長性があり、多少の欠陥があっても接合できるという利点があります。

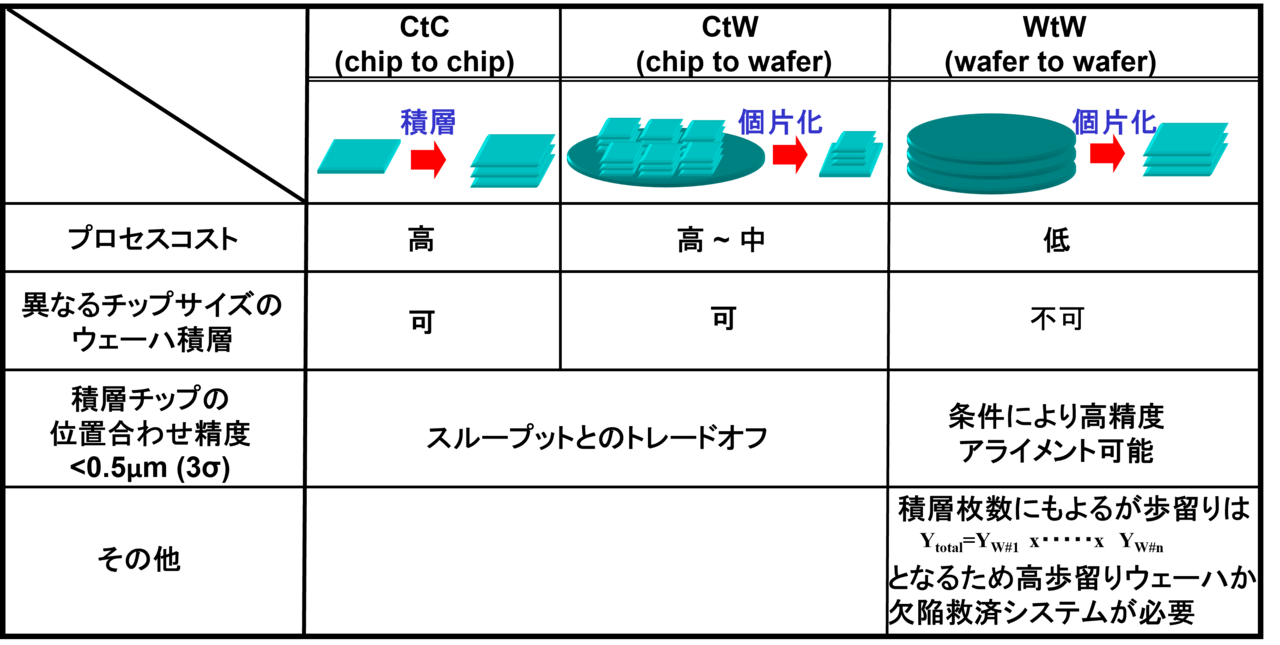

表1には三種類の積層方法について比較しました。ウェハプロセスでは、1ウェハで何個のチップ(PGD:possible good die)が取れるかが、チップコストを下げる上で非常に重要です。これが、ウェハの大口径化を進める理由です。もし、この考えを三次元の積層方法に当てはめると、例えば月産5000枚のラインでは10枚前後のウェーハもしくはウェハから取れるチップを1時間以内に処理できないとこの積層工程がボトルネックとなり、他の工程のロス分も含めて、チップコストが上がることになります。従来のPick and Place方式を使ったCoC,CoW方式でこの条件を満たすには、非常に多くの装置が必要になり、その装置を設置するクリーンルームのスペースも大きくなります。一方WoW方式は、高速で処理できる可能性はありますが、異なるサイズのチップのウェハは積層できません。また、積層すればするほど歩留まりが下がるので、メモリの場合であれば積層後に最適な欠陥救済を行えるような仕組みが必要になります。また、ウェハ製造が同一メーカーかつ同一Fabでない場合、例え同じデザインルールで作ったとしてもウェハ上におけるチップ位置が微妙に異なるため高精度のチップアライメントは難しくなので、合わせずれを吸収するようなレイアウトや配線層が必要になります。

表1. 積層方法

以上のように、生産を考えた場合の3D-IC(三次元LSI)技術は、課題が多く残っており、またどのような技術を選択するかにより、性能、歩留まり、スループットが変わってきます。先ずはアプリケーションを決め、そのためのベースLSIをどのように(何処で)作るかといったサプライチェーンを決めていくことが必要です。このような意味で、3D-IC(三次元LSI)は従来のLSI技術とは異なり、システム寄りの技術と言えると思います。弊社は東北大と低価格で三次元SoCができるように、高速でCoW積層ができる方法を研究しています。

English Site Menu

Company

Technology

Foundry service

Service case study